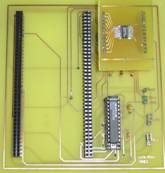

| Convertidores ADC y DAC |  CONVERTIDORES ADC Y DAC |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

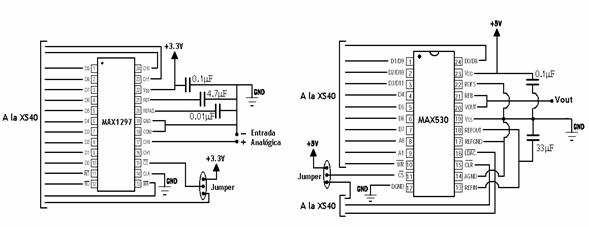

Esquema |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

MAX530 pin |

FPGA pin |

|

D0/D8 |

26 |

|

D1/D9 |

7 |

|

D2/D10 |

8 |

|

D3/D11 |

18 |

|

D4 |

20 |

|

D5 |

23 |

|

D6 |

24 |

|

D7 |

25 |

|

A0 |

27 |

|

A1 |

68 |

|

/WR |

70 |

|

/CS |

37 |

|

/LDAC |

14 |

|

/CLR |

28 |

|

VDD |

2 |

|

DGND |

52 |

|

MAX1297 pin |

FPGA pin |

|

D0 |

38 |

|

D1 |

39 |

|

D2 |

40 |

|

D3 |

41 |

|

D4 |

60 |

|

D5 |

58 |

|

D6 |

50 |

|

D7 |

56 |

|

D8 |

51 |

|

D9 |

80 |

|

D10 |

81 |

|

D11 |

35 |

|

/INT |

10 |

|

/RD |

61 |

|

/CS |

29 |

|

/WR |

62 |

|

VDD |

54 |

|

GND |

2 |

Fichero .ucf

MAX530 (DAC):

NET cs LOC = P37;

NET wr LOC = P70;

NET clr LOC = P28;

NET ldac LOC = P14;

NET a0 LOC = P27;

NET a1 LOC = P68;

NET data<0> LOC = P26;

NET data<1> LOC = P7;

NET data<2> LOC = P8;

NET data<3> LOC = P18;

NET data<4> LOC = P20;

NET data<5> LOC = P23;

NET data<6> LOC = P24;

NET data<7> LOC = P25;

MAX1297 (ADC):

NET int LOC =

P10;

NET cs LOC = P29;

NET wr LOC = P62;

NET rd LOC = P61;

NET data<0> LOC = P38;

NET data<1> LOC = P39;

NET data<2> LOC = P40;

NET data<3> LOC = P41;

NET data<4> LOC = P60;

NET data<5> LOC = P58;

NET data<6> LOC = P50;

NET data<7> LOC = P56;

NET data<8> LOC = P51;

NET data<9> LOC = P80;

NET data<10> LOC = P81;

NET data<11> LOC = P35;

Catálogos

2.

LEDs Y SENSORES DE

TEMPERATURA

3. MEMORIAS