UNIV. OF SEVILLA HARDWARE DEBUGGING SYSTEM (UNSHADES-1)

What is a Hardware Debugger?

A hardware debugger is a complete hardware emulation system for digital integrated circuits, -it can be configured with a particular digital circuit netlist and inserted into the final system- that can provide information (observability) about the internal circuit working progress during execution time. This information is directly linked to the circuit high level description for a comprehensive understanding of the circuit state at a particular execution instant called event. Due to the parallel nature of the hardware, the breakpoint concept of a software debugger is not valid, instead, the idea of execution event substitutes that concept. When a predefined condition is satisfied, the emulator produces the information for the circuit inspection. The emulation system is based on a SRAM or reprogrammable FPGA which is configured with the circuit netlist under test.

Observability is the main feature in a debugger. In Xilinx Virtex technology, It's obtained using aninternal non intrusive spying method built in the FPGA using memory resources. Controlability is also important and can be made with a insertion of the FPGA device into the final system (the circuit with the surrounding components). The control of the debugger itself is made using external pins (in our case, we use only two wires for the debugging system and it is an University of Sevilla propietary patent) as minimum external resources overhead.

Finally, using an original method developed in our group (a second patent), the register contents can be individually modified in run time giving to the hardware debugger system a new dimension. For example, a fault tolerant design test can be performed using the register modification as bit-flip injector, and generate SEU's FT maps. Current techniques are based on software simulation approaches, but using this technique a hardware accelerated system can provide results in few minutes.

What is UNSHADES?

UNSHADES is a Virtex based hardware debugging system. Using the capabilities of the Virtex device through the SelectMAP port (say Configuration, Readback and Capture) we have developed a Virtex based board and software that is intended to be a flexible and powerful Rapid Prototyping and Hardware Debugging environment. UNSHADES has been developed with the aim of being an academic platform for applications and research issues, such as Partial and Dynamic Reconfiguration of Configurable Computing systems, VLSI on digital signal processing, large parallel processing systems,...

UNSHADES takes advantage of Virtex non standard features, reaching a high level of observability and controlability with the minimum overhead of resources.

Three are the main features of UNSHADES:

1. A High-speed link with the host-PC. We have selected

the parallel port in EPP mode, that can produce dialogs between the host

PC and UNSHADES at 500 Kbyte/s or more.

2. A full controlled core for the on board oscillator.

We have introduced a DALLAS 1075 programmable oscillator and provided a

run-time control of the system-clock frequency.

3. A powerful link with parallel SelectMAP port for configuration,

readback and capturing the internal state of VIRTEX device.

This features make UNSHADES different from commertial tools:

Using the Virtex special memory cells, the registers contents are copied on them in one clock period. The capture process hasn't any effect on the circuit itself and do not affect neither the ciruit performance nor the FPGA resources count. These memory can be read of-line.

We have also developed a simple method for modifying the circuit state and the contents of the internal registers of the Virtex FPGA during execution time, from this approach we have introduced a new idea: stimulability. It means that we can insert certain values into the internal registers, and produce controlled situations of the circuit state and observe the evolution.

Finally we've developed an IP core for running the circuit step by step. Using our two-wires system the design can be run in-system at normal clock rate. After an event we can continue the analysis in an asynchronous mode step by step (system and circuit don't run now at the same clock rate). At every step, which is the circuit evolution in a single clock cycle, the information can be downloaded and a waveform can be generated. The execution can be resumed an the circuit launched at normal clock rate, but from the asynchronous system position.

A general purpose connecting port enables all VIRTEX useable pins for a particular design, allowing an easy interface with applications.

How is UNSHADES board?

UNSHADES is based on two FPGA's. The first, a XC4010XL, is a quasi-fixed programmed FPGA that works as an interface between the host PC and the board itself. The core is the EPP protocol emulator, that allows the internal modules to be managed as a memory map from the host-PC.

Address and data are sent and read as information or commands to or from the XC4010XL FPGA, and controls the Oscillator System, the SelectMAP port, general purpose IO pins and a Serial FLASH for an eventual modification of the on board program.

The second is the VIRTEX itself. VIRTEX is connected to XC4010XL for using the SelectMAP port. Board can be mounted with all Virtex PQ240 compatible package models (V50, ..., V800). All Virtex pins are free of being used as general purpose.

As an additional feature, the Boundary Scan port is available for general programmaing of both, XC4010XL and Virtex.

UNSHADES software is Windows based and user friendly tool for downloading and easy management of the bitstream file to VIRTEX or XC4010XL prom-flash. It takes the information from the Foundation 3.3i standard design flow.

It allows an easy control of the system oscillator

DS1075 with a frequency programming dialog chart as well.

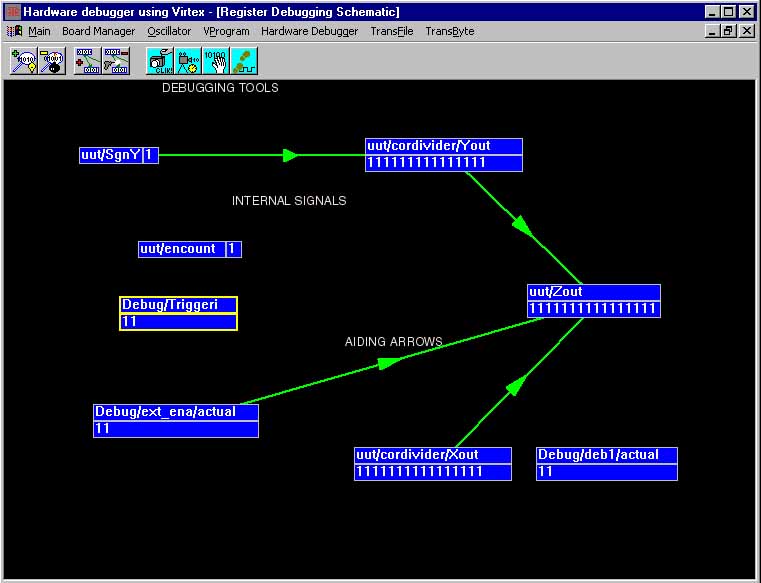

UNSHADES Software not only plays as a design downloader. It can extract ReadBack information from the FPGA and make it comprehensive for the user and procece changes in the disign state during run-time. Design information can be inspected during run-time when CAPTURE_VIRTEX macro is instantiated. Using a selection dialog chart the inspection process can be easily performed, and presented in a diagram like shown below.

Actually, software has to be run with a Unshades board attached into the parallel port. Please, send me an e-mail with your comments.

UNSHADES software tool is programmed using the information provided by Xilinx in their application notes. The tool has been developed outside JBits suite scope.

What are we doing at this moment with UNSHADES?

Now, we have a simple but powerful platform for advanced FPGA handling. We have introduced VIRTEX to undergraduate students and we have now some students making their final project (master project) using UNSHADES system, some of them in progress:

First, we are working on a JBits (from Xilinx) API for UNSHADES. We are also working on some emulation features.UNSHADES-2, a FPGA/DSP hybrid board using the Debugging concepts implemented in UNSHADES-1 is being enssambled

Papers based un UNSHADES-1

Papers and presentations in conferences related to the project

Who have made the design and development of UNSHADES?

UNSHADES has been developed by M. A. Aguirre and J.N. Tombs from the Grupo de Tecnología Electrónica (GTE) of the University of Sevilla as an academic project. We intend to use UNSHADES as general purpose lab and research platform.

Following these links you'll be in our personal web sites:

Miguel A. Aguirre (in Spanish)

Miguel A. Aguirre (in English)

visitors since

March 27th 2001 (this page is outside the commercial tours). Last change: Nov, 27th 2002